Lecture 11: Decoders

advertisement

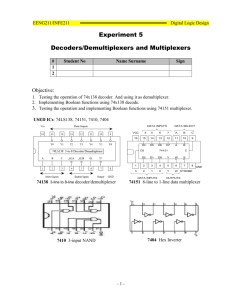

EE210: Switching Systems Lecture 11: Decoders Prof. YingLi Tian Oct. 21, 2015 Department of Electrical Engineering The City College of New York The City University of New York (CUNY) 1 1-bit Adder One-bit adder Truth Table 2 Delay in Combinational Logic Circuits 3 Comparators Compare two numbers: a > b: a = 1 and b = 0. a < b: a = 0 and b = 1. a = b: both a and b are 0 or 1 XNOR a’b ab’ Output from more significant bit XNOR: The output is 1 if the inputs are same. 4 Binary Decoders A binary decoder is a combinational type logic circuit that converts the binary code data at its input into one of a number of different output lines, one at a time producing an equivalent decimal code at its output. From a n-input binary number, the outputs will be . Active high decoder – with value 1 Active low decoder – with value 0 5 A 2-to-4 Binary Decoder http://www.electronics-tutorials.ws/combination/comb_5.html 6 Active High Decoder 7 Active Low Decoder 8 Decoder with Enable An additional input labeled "Enable" that controls the outputs of the device. The decoder outputs can be turned “on” and “off”. Active high decoder 9 A 3-to-8 decoder: 74138 EN1: active high EN2’: active low EN3’: active low Outputs: active low EN1 = 1, EN2’ = 0 and EN3’ = 0 Outputs are active low(0) The circles here indicate they are active low. 10 Combine Multiple Decoders to Form a Larger Decoder A 4-to-16 decoder using two 3-to-8 decoders. Inputs A, B, C are the inputs for each of the decoder, and D is used to select the appropriate one (D = 0 goes to the first decoder, D = 1 goes to the second decoder). http://www.electronics-tutorials.ws/combination/comb_5.html 11 Combine Multiple Decoders to Form a Larger Decoder A 5-to-32 decoder using four 3-to-8 decoders. Inputs c, d, e are the inputs for each of the decoder, and a, b are used to select the appropriate one decoder. Order: abcde 12 Implement Logic Functions using Decoders A 4-to-16 decoder using 5 2-to-4 decoders. Inputs c, d are the inputs for each of the decoder, and a, b are the inputs for the decoder that used to enable other decoders. Order: abcd 13 Implement Logic Functions using Decoders Example 5.3 (p263 - 264): Implement the following functions using decoders with OR or NAND gates. f (a, b, c) = ∑m(0, 2, 3, 7) g(a, b, c) = ∑m(1, 4, 6, 7) 14 Use a Decoder to Enable other Decoders f (a, b, c, d) = ∑m(0, 2, 7, 9, 12) g(a, b, c, d) = ∑m(1, 4, 6, 10, 15) 15 Announcement Read Chapter 5.2 Next class (Chapter 5.2): Designing Systems using Decoders 16