- No category

Biblioteka komórek standardowych TSMC 0.18µ przez Tanner CES

advertisement

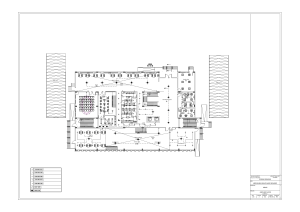

Consulting & Engineering Services www.tanner.com/ces CE-LI-CC-CE Tanner Consulting & Engineering Services tsmc018DL Digital Standard Cell Library For TSMC 0.18µ µ Process Revision A TSMC 0.18µ 0.18µ Tanner Consulting & Engineering Services delivers quality high performance ASIC and VLSI solutions for its clients, accomplished through contracted design and development efforts, consulting services, field engineering and training programs. Copyright © 2000 by Tanner Research, Inc. All rights reserved Consulting & Engineering Services www.tanner.com/ces CE-LI-CC-CE Terms and Conditions 1. Specifications: This document only includes general specifications fulfilling a common spec base among most library products. Some features may vary without descriptions in this document. It is end-user’s responsibility to confirm the specific features of the specific library product item. 2. Dedicated or customized development: If the delivery of a library product item involves dedicated or customized development work, a Statement of Work should be proposed and approved between Tanner CES and the end-user. All terms and conditions shall be specified in the document. 3. Vendor process parameters: Vendor process parameters included in technology setups and cell library products are current when a relevant library item was developed. Tanner Research is not responsible for the correctness, accuracy and integrity of data and documents provided by process vendors. It is enduser’s responsibility to obtain updated process parameters directly from the process vendor. 4. Payment: Purchase payment should be made in advance. Payment of terms may be negotiated. 5. Technical Support: Tanner CES will provide full technical support. However the intensity of support effort may vary depend on the following factors: q Larger end-user base of a popular product tends to be better supported. q If the delivered product is resulted by dedicated and customized development services, this item may likely supported under the terms and conditions as specified in the agreed Statement of Work. q Technical support may be only limited to end-users who possess a valid and current product edition. We do not provide helps to building a library with parallel functions and applications as our product line. q Technical support may be limited to Tanner CES’ resources. Our timely response shall not considered as an obligation toward end-users’ applications or project time constraints. If it is timely critical to an end-user’s project, we shall negotiate a dedicated service contract to cover the demanded technical support work. 6. Liability: All our products are developed on a best effort basis. Tanner Research is not liable for qualities and/or performances of end-users’ future projects using components provided in our product packages, or for using our recommended design methodologies. Tanner Research, Inc. Consulting & Engineering Services www.tanner.com/ces CE-LI-CC-CE 7. Non-Disclosure Agreements: Vendor process information shall be protected by an NDA between an end-user and it’s the product-related process vendor. It is not our responsibility to confirm the existence or contents of such an NDA. We always assume that the end-user has already signed NDA with the process vendor, however we may request the end-user to provide a proof of such NDA prier to the delivery of a product. On the developer side, Tanner Research is bonded by NDAs with process vendors. Upon the end-user’s demand, we may also sign an NDA with the end-user, to prevent us disclosing end-user’s name, motivation of using a specific library product, vendor selection and fabrication plans. 8. Product Ownership: By purchasing the specified product, an end-usr owns the delivered version of the product. It agrees to only use the product in projects or products that developed by itself and on its own site. The end-user will not distribute copies of data files and documents (such as library design, process technology setups, design flow and methodology, software utilities, etc.) to any third parties and its other sites. The delivered product and related software tools as well subjects to Tanner Research’s standard Terms and Conditions (below) issued along with all sales and releases of Tanner Research software and data. Terms and Conditions Tanner Research, Inc. grants a license to use this software but does not grant the right to reproduce, prepare derivative works nor distribute the software. Tanner Research, Inc. makes no representations or warranties of merchantability or fitness for any particular purpose or that the use of the software will not infringe any patents, copyrights, trademarks or other rights. Sublicensee shall not hold Tanner Research, Inc. liable for any liability or damages with respect to any claim by Sublicensee or others on account of, or arising from the Use Sublicense of the software or Tanner Research, Inc. Program(s) or Maintenance And Enhancement Services; Sublicensee agrees to indemnify Tanner Research, Inc., hold harmless and defend Tanner Research, Inc. against any and all claims arising out of the Use Sublicense, including, without limiting the generality of the foregoing, against any damages, losses or liabilities whatsoever with respect to death or injury to person or damage to property arising from or out of the possession, use or operation of software or Tanner Research, Inc. Program(s) or Maintenance And Enhancement Services; Use Sublicensee shall maintain in confidence and exercise due care and diligence in protecting Tanner Research, Inc.’s proprietary information, including without limitation the software and Tanner Research, Inc. Program(s) and shall not disclose any of such information to others; Use Sublicensee shall take appropriate action with its employees, consultants, agents and representatives to satisfy its confidentiality obligation under the Use Sublicense with respect to maintaining the above degree of protection for the software and Tanner Research, Inc. Program(s); Tanner Research, Inc. grants the Use Sublicensee only the right to use the software and Tanner Research, Inc. Program(s) internally. Duplication or copying, in whole or part, alteration, modification, reverse engineering, reverse compilation or reverse assembly of the software or Tanner Research, Inc. Program(s) is strictly prohibited and such acts will result in automatic termination of the Use Sublicense; and Use Sublicensee’s rights in the software and Tanner Research, Inc. Program(s) shall not be transferable and shall not be sold, further licensed, encumbered or pledged. Copyright 2000 by Tanner Research, Inc. All rights reserved. Tanner Research, Inc. Consulting & Engineering Services www.tanner.com/ces CE-LI-CC-CE Table of Contents 2x2 Input AND-OR gate: ......................................................................................AO22 2x2 Input AND-NOR Gate: ..................................................................................AOI22 1X-Drive Non-Inverting Buffer: ...........................................................................BUF1 4X-Drive Non-Inverting Buffer: ...........................................................................BUF4 4X-Drive Inverter: ................................................................................................BUFI4 Tri-State Inverter: ................................................................................................ BUFZ D Flip-Flop:.............................................................................................................. DFF D Flip-Flop With Asynchronous Clear: .............................................................. DFFC D Flip-Flop With Preset: .......................................................................................DFFP D Flip-Flop With Preset & Asynchronous Clear:............................................ DFFPC Inverter: .................................................................................................................... INV Dual Inverter: ......................................................................................................... INV2 Tri-State Inverter:...................................................................................................INVZ Latch:....................................................................................................................... LAT Latch With Clear: ................................................................................................. LATC Latch With Preset: ................................................................................................LATP Latch With Preset & Clear: ............................................................................... LATPC 2-Input Multiplexer: ............................................................................................. MUX2 2-Input NAND Gate: ...........................................................................................NAND2 2-Input NAND Gate With Complementary Output:....................................... NAND2C 3-Input NAND Gate: ...........................................................................................NAND3 3-Input NAND Gate With Complementary Output:....................................... NAND3C 4-Input NAND Gate: ...........................................................................................NAND4 4-Input NAND Gate With Complementary Output:....................................... NAND4C Tanner Research, Inc. Consulting & Engineering Services www.tanner.com/ces CE-LI-CC-CE 2-Input NOR Gate: ............................................................................................... NOR2 2-Input NOR Gate With Complementary Output: ........................................... NOR2C 3-Input NOR Gate: ............................................................................................... NOR3 3-Input NOR Gate With Complementary Output: ........................................... NOR3C 4-Input NOR Gate: ............................................................................................... NOR4 4-Input NOR Gate With Complementary Output: ........................................... NOR4C Schmitt Trigger Inverter:.......................................................................................SINV 2-Input Exclusive-NOR Gate:............................................................................XNOR2 2-Input Exclusive-OR Gate: ................................................................................ XOR2 Tanner Research, Inc. 2X2 Input AND-OR Description: 2 X 2 Input AND-OR Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol A B AO22 Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: AO22 File: tsmc018DL.tdb Cell: AO22 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table A*B 0 1 X Out C D Height 7.33µ Width 5.04µ C*D 0 X 1 Area Capacitance Out 0 1 1 Equivalent Gate Drive 1X Logic Equation Out = (A × B) + (C × D) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A AO22 Page 1 of 4 2X2 Input AND-OR AO22 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A AO22 Page 2 of 4 2X2 Input AND-OR Schematic AO22 AO22 Vdd A M0 M2 W =2.0 0 u L=0 .18u W =2.0 0 u L=0 .18u M3 W =2.0 0 u L=0 .18u B 1 C W =2.0 0 u L=0 .18u M1 D 2 B W =0.8 0 u L=0 .18u W =0.8 0 u L=0 .18u C M5 M7 3 A W =2.0 0 u L=0 .18u W =0.8 0 u L=0 .18u Out M9 4 W =0.8 0 u L=0 .18u D M6 M4 W =0.8 0 u L=0 .18u M8 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A AO22 Page 3 of 4 2X2 Input AND-OR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. AO22 Rev. A AO22 Page 4 of 4 2X2 Input AND-NOR Description: 2 X 2 Input AND-NOR Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol A B Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: AOI22 File: tsmc018DL.tdb Cell: AOI22 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table A*B 0 1 X Out C D AOI22 Height 7.33µ Width 3.60µ C*D 0 X 1 Area Capacitance Out 1 0 0 Equivalent Gate Drive 1X Logic Equation Out = (A × B) + (C × D) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A AOI22 Page 1 of 4 2X2 Input AND-NOR AOI22 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A AOI22 Page 2 of 4 2X2 Input AND-NOR Schematic AOI22 AOI22 Vdd M0 A W=2.00u L=0.18u M2 W=2.00u L=0.18u W=2.00u L=0.18u M3 W=2.00u L=0.18u B 1 M1 C D W=0.80u L=0.18u B W=0.80u L=0.18u C M5 M7 3 A Out 4 W=0.80u L=0.18u D M6 W=0.80u L=0.18u M8 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A AOI22 Page 3 of 4 2X2 Input AND-NOR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. AOI22 Rev. A AOI22 Page 4 of 4 Non-Inverting Buffer Description: Non-Inverting Buffer Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol A BUF1 Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: Buf1 File: tsmc018DL.tdb Cell: Buf1 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table A 0 1 Out Height 7.33µ Width 2.88µ Capacitance Out 0 1 Area Equivalent Gate Drive 1X Logic Equation Out = A Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUF1 Page 1 of 4 Non-Inverting Buffer BUF1 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUF1 Page 2 of 4 Non-Inverting Buffer Schematic BUF1 BUF1 Vdd M0 A 1 W =2 .0 0 u M 2 L=0 .1 8 u W =2 .0 0 u L=0 .1 8 u W =0 .8 0 u L=0 .1 8 u W =0 .8 0 u L=0 .1 8 u M1 Out M3 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUF1 Page 3 of 4 Non-Inverting Buffer Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. BUF1 Rev. A BUF1 Page 4 of 4 4X-Drive Buffer Description: BUF4 4X-Non-Inverting Buffer Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol 4 A Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: BUF4 File: tsmc018DL.tdb Cell: BUF4 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table A 0 1 Out Height 7.33µ Width 5.04µ Capacitance Out 0 1 Area Equivalent Gate Drive 4X Logic Equation Out = A Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUF4 Page 1 of 4 4X-Drive Buffer BUF4 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUF4 Page 2 of 4 4X-Drive Buffer Schematic BUF4 BUF4 Vdd M0 W =2 .0 0 u M 2 L=0 .18u W =8 .0 0 u L=0 .18u W =0 .8 0 u L=0 .18u W =3 .2 0 u L=0 .18u Out 1 A M1 M3 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUF4 Page 3 of 4 4X-Drive Buffer Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. BUF4 Rev. A BUF4 Page 4 of 4 4X-Drive Inverter Description: 4X-Non-Inverting Buffer Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol 4 A BUFI4 Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: BUFI4 File: tsmc018DL.tdb Cell: BUFI4 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table A 0 1 Out Height 7.33µ Width 2.88µ Capacitance Out 1 0 Area Equivalent Gate Drive 4X Logic Equation Out = A Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUFI4 Page 1 of 4 4X-Drive Inverter BUFI4 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUFI4 Page 2 of 4 4X-Drive Inverter Schematic BUFI4 BUFI4 Vdd M0 W =8.00u L=0 .18u A Out W =3.20u L=0 .18u M1 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUFI4 Page 3 of 4 4X-Drive Inverter Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. BUFI4 Rev. A BUFI4 Page 4 of 4 Tri-State Buffer Description: BUFZ Tri-State Buffer Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: BUFZ File: tsmc018DL.tdb Cell: BUFZ TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table OEB A Primitive Set: OEB 1 0 0 Out Height 7.33µ Width 5.04µ A X 0 1 Area Capacitance Out Z 0 1 Equivalent Gate Drive 1X Logic Equation Out = A Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUFZ Page 1 of 4 Tri-State Buffer BUFZ This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUFZ Page 2 of 4 Tri-State Buffer Schematic BUFZ BUFZ Vdd W =2.00u L=0.18u M1 W =2.00u L=0.18u M0 M3 Data M4 2 OEB 1 M5 W =0.80u L=0.18u OEB 3 OEB W =2.00u L=0.18u W =0.80u L=0.18u M7 W =2.00u L=0.18u M2 W =2.00u L=0.18u Out W =0.80u L=0.18u W =0.80u L=0.18u Data M6 W =0.80u M 9 L=0.18u M8 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A BUFZ Page 3 of 4 Tri-State Buffer Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. BUFZ Rev. A BUFZ Page 4 of 4 D Flip-Flop DFF Description: D Flip-Flop Library: Tanner tsmc018DL Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: DFF File: tsmc018DL.tdb Cell: DFF TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol Data D Clk Truth Table Q Q Q QB Height 7.33µ Clk 1 0 ↑ ↑ Width 13.68µ Data X X 0 1 Q(t+1) Q(t) Q(t) 0 1 Capacitance QB(t+1) QB(t) QB(t) 1 0 Area Equivalent Gate Drive 1X Logic Equation I(t + 1) = Data × Clk + (I(t ) × Clk ) Q(t + 1) = (I (t ) × Clk ) + Q(t ) × Clk QB(t + 1) = Q(t + 1) ( ) ( ) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFF Page 1 of 4 D Flip-Flop DFF This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFF Page 2 of 4 D Flip-Flop Schematic DFF dff Vdd 3 C T6 W =2 .0 0 u L=0 .1 8 u W =2 .0 0 u L=0 .1 8 u T9 7 CB T1 0 W =2 .0 0 u L=0 .1 8 u 9 T1 3 4 W =0 .8 0 u L=0 .1 8 u CB T7 DATA 5 W =0 .8 0 u L=0 .1 8 u T8 T1 6 CB 6 W =2 .0 0 u L=0 .1 8 u 11 T1 2 12 C T2 0 W =2 .0 0 u L=0 .1 8 u T2 3 W =2 .0 0 u L=0 .1 8 u T1 8 T2 5 W =2 .0 0 u L=0 .1 8 u T2 7 W =2 .0 0 u L=0 .1 8 u W =2 .0 0 u L=0 .1 8 u 13 W =0 .8 0 u L=0 .1 8 u T1 7 W =0 .8 0 u L=0 .1 8 u T1 9 10 C T1 4 T1 1 8 W =2 .0 0 u L=0 .1 8 u W =0 .8 0 u L=0 .1 8 u W =0 .8 0 u L=0 .1 8 u C W =2 .0 0 u L=0 .1 8 u T1 5 QB W =0 .8 0 u L=0 .1 8 u CB W =0 .8 0 u L=0 .1 8 u T2 1 W =0 .8 0 u L=0 .1 8 u W =0 .8 0 u T2 4 L=0 .1 8 u W =0 .8 0 u L=0 .1 8 u T2 6 W =0 .8 0 u L=0 .1 8 u T2 8 T2 2 Gnd Q W =2 .0 0 u L=0 .1 8 u T5 DATA Vdd T1 W =2 .0 0 u L=0 .1 8 u T3 CB CLK C W =0 .8 0 u L=0 .1 8 u T2 W =2 .0 0 u L=0 .1 8 u W =0 .8 0 u L=0 .1 8 u T4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFF Page 3 of 4 D Flip-Flop Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. DFF Rev. A DFF Page 4 of 4 D Flip-Flop AC Description: DFFC D Flip-Flop with Asynchronous Clear Library: Tanner tsmc018DL Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: DFFC File: tsmc018DL.tdb Cell: DFFC TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Truth Table ClB Logic Symbol D Data Clk Cl Q Q Q QB Height 7.33µ Clk X 1 0 ↑ ↑ ClB 0 1 1 1 1 Width 15.84µ Data X X X 0 1 Capacitance Q(t+1) 0 Q(t) Q(t) 0 1 Area QB(t+1) 1 QB(t) QB(t) 1 0 Equivalent Gate Drive 1X Logic Equation I(t + 1) = Data × Clk + (I(t ) × Clk ) × ClB Q(t + 1) = (I (t ) × Clk ) + Q(t ) × Clk × ClB QB(t + 1) = Q(t + 1) ( ) ( ) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFFC Page 1 of 4 D Flip-Flop AC DFFC This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFFC Page 2 of 4 D Flip-Flop AC Schematic DFFC dffc Vdd W =2.00u L=0.18u T10 6 CB T14 W =2.00u L=0.18u CB T15 9 T18 W =2.00u L=0.18u 11 W =2.00u L=0.18u T16 4 W =0.80u L=0.18u T7 5 DATA 10 W =0.80u T8 W =0.80u L=0.18u W =0.80u L=0.18u C T11 7 8 T19 T17 T13 W =2.00u L=0.18u T29 W =2.00u L=0.18u T31 W =2.00u T33 L=0.18u W =2.00u L=0.18u 16 W =2.00u L=0.18u T24 C 17 W =0.80u L=0.18u C T21 14 W =0.80u L=0.18u T26 12 CLBT20 13 W =0.80u L=0.18u W =2.00u L=0.18u W =2.00u L=0.18u T23 CB L=0.18u T12 CLB CB W =2.00u L=0.18u W =2.00u L=0.18u CBT25 W =0.80u L=0.18u W =0.80u L=0.18u W =0.80u T30 L=0.18u T1 W =0.80u L=0.18u T34 15 W =0.80u L=0.18u T28 Vdd W =2.00u L=0.18uT3 CB CLK W =0.80u L=0.18u T32 T27 W =0.80u L=0.18u T22 Gnd QB W =0.80u L=0.18u Q C W =2.00u L=0.18u CLB 3 T9 CLB T6 W =2.00u L=0.18u CLB T5 DATA W =0.80u L=0.18u T2 W =2.00u L=0.18u C W =0.80u L=0.18u T4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFFC Page 3 of 4 D Flip-Flop AC Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. DFFC Rev. A DFFC Page 4 of 4 D Flip-Flop Preset Description: DFFP D Flip-Flop with Preset Library: Tanner tsmc018DL Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: DFFP File: tsmc018DL.tdb Cell: DFFP TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol D Data Clk Pr Truth Table Q Q Q QB PrB Height 7.33µ Clk X 1 0 ↑ ↑ PrB 0 1 1 1 1 Width 15.12µ Data X X X 0 1 Capacitance Q(t+1) 1 Q(t) Q(t) 0 1 Area QB(t+1) 0 QB(t) QB(t) 1 0 Equivalent Gate Drive 1X Logic Equation I(t + 1) = Data × Clk + (I(t ) × Clk ) × PrB Q(t + 1) = (I(t ) × Clk ) + Q(t ) × Clk × PrB QB(t + 1) = Q(t + 1) ( ) ( ) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFFP Page 1 of 4 D Flip-Flop Preset DFFP This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFFP Page 2 of 4 D Flip-Flop Preset Schematic DFFP DFFP Vdd C T6 W =2.00u L=0.18u W =2.00u L=0.18u T9 6 CB W =2.00u L=0.18u T10 4 W =0.80u L=0.18u T7 DATA 5 W =0.80u L=0.18u C T8 7 W =0.80u L=0.18u CB W =0.80u L=0.18u 8 12 T20 13 C T22 W =2.00u L=0.18u T25 W =2.00u L=0.18u T27 W =2.00u L=0.18uT29 W =2.00u L=0.18u T31 W =0.80u L=0.18u CB W =0.80u L=0.18u T23 W =0.80u L=0.18u W =2.00u L=0.18u W =2.00u L=0.18u PRB W =0.80u L=0.18uT26 T24 QB W =0.80u L=0.18u W =0.80u L=0.18u T28 14 W =0.80u L=0.18u T32 T30 Gnd T3 W =0.80u L=0.18u T2 T21 15 T19 T15 W =2.00u L=0.18u CB CLK W =2.00u L=0.18u W =0.80u L=0.18u C W =0.80u L=0.18u Vdd W =2.00u L=0.18u T18 W =2.00u L=0.18u 11 T14 T12 T1 T17 10 9 T11 W =0.80u L=0.18u W =2.00u L=0.18u Q CB W =2.00u T16 L=0.18u T13 PRB 3 9 PRB W =2.00u L=0.18u T5 DATA W =0.80u L=0.18u C T4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFFP Page 3 of 4 D Flip-Flop Preset Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. DFFP Rev. A DFFP Page 4 of 4 D Flip-Flop P/AC Description: DFFPC D Flip-Flop with Preset and Asynchronous Clear Library: Tanner tsmc018DL Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: DFFPC File: tsmc018DL.tdb Cell: DFFPC TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol ClB D Data Clk Cl Pr Truth Table Q Q Q QB PrB Height 7.33µ Clk X X X X 1 0 ↑ ↑ PrB 0 1 0 ↑ 1 1 1 1 ClB 1 0 0 ↑ 1 1 1 1 Width 18.00µ Data X X X X X X 0 1 Capacitance Q(t+1) 1 0 1 ? Q(t) Q(t) 0 1 Area QB(t+1) 0 1 1 ? QB(t) QB(t) 1 0 Equivalent Gate Drive 1X Logic Equation I(t + 1) = Data × Clk + (I(t ) × Clk ) × ClB × PrB Q(t + 1) = (I (t ) × Clk ) + Q(t ) × Clk × ClB × PrB QB(t + 1) = Q(t + 1) ( ) ( ) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFFPC Page 1 of 4 D Flip-Flop P/AC DFFPC This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFFPC Page 2 of 4 D Flip-Flop P/AC Schematic DFFPC DFFPC Vdd CB T8 CB W =0.80u L=0.18u T15 9 W =2.00u L=0.18u T16 W =2.00u T19 L=0.18u 12 W =2.00u T21 L=0.18u CB CB W =0.80u L=0.18u C T11 7 10 W =0.80u L=0.18u 11 13 CLBT22 14 T17 T12 8 W =0.80u L=0.18u W =0.80u L=0.18u C T23 15 T18 W =0.80u L=0.18u T13 W =2.00u L=0.18u T25 CLB W =2.00u L=0.18u T20 PRB 6 W =0.80u L=0.18u T7 5 DATA T10 W =2.00u L=0.18u W =2.00u L=0.18u T26 W =2.00u L=0.18u T28 18 T33 W =2.00u L=0.18u T34 W =2.00u T37 L=0.18u W =2.00u L=0.18u 19 W =0.80u L=0.18u W =0.80u L=0.18u PRB CBT27 W =0.80u L=0.18u W =0.80u L=0.18u 17 T36 T29 W =0.80u L=0.18u 16 QB T35 W =0.80u T32 L=0.18u W =0.80u L=0.18u W =0.80u L=0.18u T38 W =0.80u L=0.18u T30 W =2.00u L=0.18u T3 W =2.00u L=0.18u CB W =0.80u L=0.18u T2 W =2.00u L=0.18u C W =0.80u L=0.18u Gnd Vdd CLK T31 W =2.00u L=0.18u T24 T1 W =2.00u L=0.18u Q 4 W =2.00u L=0.18u T14 CLB C W =2.00u L=0.18u CLB 3 T9 PRB T6 W =2.00u L=0.18u CLB T5 DATA W =0.80u L=0.18u C T4 TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A DFFPC Page 3 of 4 D Flip-Flop P/AC Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. DFFPC Rev. A DFFPC Page 4 of 4 Inverter INV Description: Inverter Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol A Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: INV File: tsmc018DL.tdb Cell: INV TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table A 0 1 Out Height 7.33µ Width 1.44µ Capacitance Out 1 0 Area Equivalent Gate Drive 1X Logic Equation Out = A Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A INV Page 1 of 4 Inverter INV This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A INV Page 2 of 4 Inverter Schematic INV INV Vdd M0 W=2.00u L=0.18u A Out W=0.80u L=0.18u M1 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A INV Page 3 of 4 Inverter Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. INV Rev. A INV Page 4 of 4 Dual Inverter INV2 Description: Dual Inverter Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: INV2 File: tsmc018DL.tdb Cell: INV2 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol Truth Table A I0 O0 Out1 B I1 O1 Out2 Height 7.33µ A 0 0 1 1 Width 2.88µ B 0 1 0 1 Out1 1 1 0 0 Area Capacitance Out2 1 0 1 0 Equivalent Gate Drive 1X Logic Equation Out1 = A Out2 = B Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A INV2 Page 1 of 4 Dual Inverter INV2 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A INV2 Page 2 of 4 Dual Inverter Schematic INV2 INV2 Vdd T1 A Vdd W =2.0 0 u L=0 .1 8 u W =0.8 0 u L=0 .1 8 u T2 Gnd T3 Out1 B W =2.0 0 u L=0 .1 8 u W =0.8 0 u L=0 .1 8 u Out2 T4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A INV2 Page 3 of 4 Dual Inverter Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. INV2 Rev. A INV2 Page 4 of 4 Tri-State Inverter Description: Tri-State Inverter Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: INVZ File: tsmc018DL.tdb Cell: INVZ TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table OEB Logic Symbol A INVZ OEB 1 0 0 Out Height 7.33µ Width 4.32µ A X 0 1 Area Capacitance Out Z 1 0 Equivalent Gate Drive 1X Logic Equation Out = A Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A INVZ Page 1 of 4 Tri-State Inverter INVZ This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A INVZ Page 2 of 4 Tri-State Inverter Schematic INVZ INVZ Vdd Data W =2.00u L=0.18u T3 2 OEB T4 W =2.00u L=0.18u Data W =2.00u L=0.18u T7 4 OEB T8 W =0.80u L=0.18u W =2.00u L=0.18u T1 W =2.00u L=0.18u W =0.80u L=0.18u T5 Out T9 3 OEB 1 5 W =0.80u L=0.18u T2 Data W =0.80u L=0.18u T6 Data W =0.80u L=0.18u T10 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A INVZ Page 3 of 4 Tri-State Inverter Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. INVZ Rev. A INVZ Page 4 of 4 Latch LAT Description: Latch Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: LAT File: tsmc018DL.tdb Cell: LAT TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol Truth Table Data D Q Q GB G Q QB Height 7.33µ GB 0 0 1 Width 6.48µ Data 0 1 X Q(t+1) 0 1 Q(t) Area Capacitance QB(t+1) 1 0 QB(t) Equivalent Gate Drive 1X Logic Equation Q(t + 1) = Data × GB + (Q(t) × GB) QB(t + 1) = Q(t + 1) ( ) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LAT Page 1 of 4 Latch LAT This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LAT Page 2 of 4 Latch Schematic LAT LAT Vdd Vdd T1 W =2.00u L=0.18u T3 GBi W =0.80u W =0.80u L=0.18u T2 W =2.00u L=0.18u T5 Data 3 G GB W =2.00u L=0.18u L=0.18u GBi T6 4 T4 G Gnd W =2.00u L=0.18u W =0.80u L=0.18u T7 5 Data T9 G GBi T10 W =2.00u L=0.18u W =2.00u L=0.18u T13 W =0.80u L=0.18u W =2.00u L=0.18u W =0.80u L=0.18u T11 QB W =0.80u L=0.18u Q T14 W =0.80u L=0.18u T8 T12 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LAT Page 3 of 4 Latch Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. LAT Rev. A LAT Page 4 of 4 Latch with Clear Description: LATC Latch with Clear Library: Tanner tsmc018DL Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: LATC File: tsmc018DL.tdb Cell: LATC TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol Truth Table ClB Data D GB G Cl Q Q Q QB Height 7.33µ GB X 0 0 1 ClB 0 1 1 1 Width 7.92µ Data X 0 1 X Capacitance Q(t+1) 0 0 1 Q(t) Area QB(t+1) 1 1 0 QB(t) Equivalent Gate Drive 1X Logic Equation Q(t + 1) = Data × GB + (Q(t ) × GB) × ClB QB(t + 1) = Q(t + 1) ( ) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LATC Page 1 of 4 Latch with Clear LATC This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LATC Page 2 of 4 Latch with Clear Schematic LATC LATC Vdd W =2 .00u L=0 .18u T7 T1 1 W =2 .00u L=0 .18u T15 W =2 .00u L=0 .18u T1 6 W =2 .00u L=0 .18u 4 W =2 .00u L=0 .18u T5 Data 3 W =2 .00u L=0 .18u T8 GBi 5 W =0 .80u L=0 .18u G T6 W =0 .80u L=0 .18u T9 T1 2 G GBi W =2 .00u L=0 .18u ClB 7 T1 3 W =0 .80u L=0 .18u T1 7 Q W =0 .80u L=0 .18u W =0 .80u L=0 .18u T1 0 T1 4 Vdd W =2 .00u L=0 .18u Gnd T3 G GB QB T1 8 W =0 .80u L=0 .18u 6 T1 W =0 .80u L=0 .18u GBi W =0 .80u L=0 .18u T2 W =2 .00u L=0 .18u W =0 .80u L=0 .18u T4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LATC Page 3 of 4 Latch with Clear Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. LATC Rev. A LATC Page 4 of 4 Latch with Preset Description: LATP Latch with Preset Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: LATP File: tsmc018DL.tdb Cell: LATP TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol Data D GB G Pr Truth Table Q Q Q QB GB X 0 0 1 PrB 0 1 1 1 Data X 0 1 X Capacitance Q(t+1) 1 0 1 Q(t) QB(t+1) 0 1 0 QB(t) PrB Height 7.33µ Logic Equation ( Width 7.29µ ) ( Area Q(t + 1) = Data × GB + (Q(t ) × GB) + PrB QB(t + 1) = Q(t + 1) Equivalent Gate Drive 1X ) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LATP Page 1 of 4 Latch with Preset LATP This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LATP Page 2 of 4 Latch with Preset Schematic LATP LATP Vdd W =2.00u L=0.18u T5 Data T9 W =2.00u L=0.18u T13 W =2.00u L=0.18u PrB 3 GBi W =2.00u L=0.18u T6 4 G W =0.80u L=0.18u T7 5 Data G GBi T10 W =2.00u L=0.18u W =0.80u L=0.18u PrB W =0.80u L=0.18u W =2.00u L=0.18u Q T16 6 T11 W =0.80u L=0.18u QB W =0.80u L=0.18u W =0.80u L=0.18u T8 T14 T15 T12 Gnd Vdd T1 W =2.00u L=0.18u T3 W =2.00u L=0.18u G GB W =0.80u L=0.18u T2 W =0.80u L=0.18u GBi T4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LATP Page 3 of 4 Latch with Preset Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. LATP Rev. A LATP Page 4 of 4 Latch with Pre/Clr Description: LATPC Latch with Preset and Clear Library: Tanner tsmc018DL Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: LATPC File: tsmc018DL.tdb Cell: LATPC TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol Truth Table Capacitance ClB Data D GB G Cl Pr Q Q Q QB PrB Height 7.33µ GB X X 1 0 0 1 PrB 0 1 ↑ 1 1 1 Width 9.36µ ClB X 0 ↑ 1 1 1 Data 1 X X 0 1 X Q(t+1) 1 0 ? 0 1 Q(t) Area QB(t+1) 0 1 ? 1 0 QB(t) Equivalent Gate Drive 1X Logic Equation Q(t + 1) = Data × GB + (Q(t ) × GB) × ClB × PrB QB(t + 1) = Q(t + 1) (( ) ) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LATPC Page 1 of 4 Latch with Pre/Clr LATPC This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LATPC Page 2 of 4 Latch with Pre/Clr Schematic LATPC LATPC Vdd W =2 .0 0 u L=0.18u T5 Data 3 T6 GBi 4 G W =0 .8 0 u L=0.18u T7 8 Data W =2 .0 0 u L=0.18u T9 Q T10 G GBi 5 T16 Q W =0 .8 0 u L=0.18u T12 W =2 .0 0 u L=0.18u W =0 .8 0 u L=0.18u T13 ClB W =0 .8 0 u L=0.18u T14 Q T20 7 PrB W =0 .8 0 u L=0.18u T18 Gnd Vdd T3 W =2 .0 0 u L=0.18u G W =0 .8 0 u L=0.18u T2 T19 PrB T17 QB W =2 .0 0 u L=0.18u W =2 .0 0 u L=0.18u W =0 .8 0 u L=0.18u T11 T8 GB 6 W =2 .0 0 u L=0.18u W =2 .0 0 u L=0.18u W =2 .0 0 u L=0.18u T15 W =0 .8 0 u L=0.18u W =0 .8 0 u L=0.18u T1 W =2 .0 0 u L=0.18u W =0 .8 0 u L=0.18u GBi T4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A LATPC Page 3 of 4 Latch with Pre/Clr Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. LATPC Rev. A LATPC Page 4 of 4 2-Input Multiplexer Description: 2-Input Multiplexer Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol A D0 B D1 Y MUX2 Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: MUX2 File: tsmc018DL.tdb Cell: MUX2 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table Sel 0 1 Out Capacitance Out B A Sel S0 Height 7.33µ Logic Equation Out = (A × Sel Width 5.04µ )+ Area Equivalent Gate Drive 1X (B × Sel ) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A MUX2 Page 1 of 4 2-Input Multiplexer MUX2 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A MUX2 Page 2 of 4 2-Input Multiplexer Schematic MUX2 MUX2 Vdd Vdd G T1 Sel W=2.00u L=0.18u W=0.80u L=0.18u T2 W=2.00u L=0.18u T3 2 G A T4 3 A W=0.80u L=0.18u 5 T6 B Sel T8 W=2.00u L=0.18u T9 W=0.80u L=0.18u T11 W=0.80u L=0.18u B T7 4 Gnd W=2.00u L=0.18u W=2.00u L=0.18u T5 Sel W=0.80u L=0.18u Out T12 6 G W=2.00u L=0.18u W=0.80u L=0.18u T10 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A MUX2 Page 3 of 4 2-Input Multiplexer Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. MUX2 Rev. A MUX2 Page 4 of 4 2-Input NAND Description: NAND2 2-Input NAND Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NAND2 File: tsmc018DL.tdb Cell: NAND2 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol Truth Table A 0 X 1 A Out B Height 7.33µ Width 2.16µ B X 0 1 Area Capacitance Out 1 1 0 Equivalent Gate Drive 1X Logic Equation Out = A X B Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NAND2 Page 1 of 4 2-Input NAND NAND2 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NAND2 Page 2 of 4 2-Input NAND Schematic NAND2 NAND2 Vdd M0 W =2.00u M 1 L=0.18u W =2.00u L=0.18u A O ut W =1.20u L=0.18u M2 1 B W =1.20u L=0.18u M3 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NAND2 Page 3 of 4 2-Input NAND Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. NAND2 Rev. A NAND2 Page 4 of 4 2-Input NAND / AND Description: NAND2C 2-Input NAND Gate with Complementary Output Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NAND2C File: tsmc018DL.tdb Cell: NAND2C TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol Truth Table A 0 X 1 A Out1 B Out2 Height 7.33µ Width 2.88µ B X 0 1 Out1 1 1 0 Area Capacitance Out2 0 0 1 Equivalent Gate Drive 1X Logic Equation Out1 = A × B Out2 = A × B Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NAND2C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 1 of 4 2-Input NAND / AND NAND2C This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NAND2C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 2 of 4 2-Input NAND / AND Schematic NAND2C NAND2C Vdd A W =2 .00u L=0.1 8 u T1 B T2 W =2 .00u L=0.1 8 u T5 W =1 .20u L=0.1 8 u A T3 W =0 .80u L=0.1 8 u Out2 T6 1 B W =2 .00u L=0.1 8 u W =1 .20u L=0.1 8 u Out1 T4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NAND2C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 3 of 4 2-Input NAND / AND Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library NAND2C Rev. A NAND2C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 4 of 4 3-Input NAND Description: NAND3 3-Input NAND Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NAND3 File: tsmc018DL.tdb Cell: NAND3 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol A B C Truth Table A 0 X X 1 Out Height 7.33µ Width 6.48µ B X 0 X 1 C X X 0 1 Area Capacitance Out 1 1 1 0 Equivalent Gate Drive 1X Logic Equation Out = A × B × C Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NAND3 Page 1 of 4 3-Input NAND NAND3 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NAND3 Page 2 of 4 3-Input NAND Schematic NAND3 NAND3 Vdd M 0 A W =2 .0 0 u L=0.1 8 u M 1 W =2 .0 0 u L=0.1 8 u M 2 W =2 .0 0 u L=0.1 8 u O ut W =2 .0 0 u L=0.1 8 u M 3 1 B W =2 .0 0 u L=0.1 8 u M 4 W =2 .0 0 u L=0.1 8 u C M 5 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NAND3 Page 3 of 4 3-Input NAND Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. NAND3 Rev. A NAND3 Page 4 of 4 3-Input NAND / AND Description: NAND3C 3-Input NAND Gate with Complementary Output Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NAND3C File: tsmc018DL.tdb Cell: NAND3C TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol A B C Truth Table A 0 X X 1 Out1 Out2 Height 7.33µ Width 7.20µ B X 0 X 1 C X X 0 1 Capacitance Out1 1 1 1 0 Area Out2 0 0 0 1 Equivalent Gate Drive 1X Logic Equation Out1 = A × B × C Out2 = A × B × C Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NAND3C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 1 of 4 3-Input NAND / AND NAND3C This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NAND3C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 2 of 4 3-Input NAND / AND Schematic NAND3C NAND3C Vdd M0 W =2.00u M 1 L=0.1 8 u W =2.00u M 2 L=0.1 8 u W =2.00u L=0.1 8 u M3 W =2.00u L=0.1 8 u A M6 W =0.80u L=0.1 8 u M7 1 B Out1 O ut2 W =2.00u L=0.1 8 u W =2.00u L=0.1 8 u M5 W =2.00u L=0.1 8 u C M4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NAND3C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 3 of 4 3-Input NAND / AND Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library NAND3C Rev. A NAND3C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 4 of 4 4-Input NAND Description: NAND4 4-Input NAND Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NAND4 File: tsmc018DL.tdb Cell: NAND4 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol A B Truth Table A 0 X X X 1 Out C D Height 7.33µ Width 8.64µ B X 0 X X 1 C X X 0 X 1 D X X X 0 1 Area Capacitance Out 1 1 1 1 0 Equivalent Gate Drive 1X Logic Equation Out = A × B × C × D Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NAND4 Page 1 of 4 4-Input NAND NAND4 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NAND4 Page 2 of 4 4-Input NAND Schematic NAND4 NAND4 Vdd T1 A W =2.00u L=0.18u W =2.00u L=0.18u T2 B T3 C W =2.00u L=0.18u T4 D W =2.00u L=0.18u A W =2.00u L=0.18u Out T5 1 B W =2.00u L=0.18u T6 2 W =2.00u L=0.18u C T7 3 D W =2.00u L=0.18u T8 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NAND4 Page 3 of 4 4-Input NAND Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. NAND4 Rev. A NAND4 Page 4 of 4 4-Input NAND / AND Description: NAND4C 4-Input NAND Gate with Complementary Output Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NAND4C File: tsmc018DL.tdb Cell: NAND4C TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol A B Truth Table A 0 X X X 1 Out1 C D Out2 Height 7.33µ Width 9.00µ B X 0 X X 1 C X X 0 X 1 D X X X 0 1 Capacitance Out1 1 1 1 1 0 Area Out2 0 0 0 0 1 Equivalent Gate Drive 1X Logic Equation Out1 = A × B × C × D Out2 = A × B × C × D Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NAND4C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 1 of 4 4-Input NAND / AND NAND4C This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NAND4C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 2 of 4 4-Input NAND / AND Schematic NAND4C NAND4C Vdd M 0 A W =2 .0 0 u M 1 L=0.1 8 u W =2 .0 0 u M 2 L=0.1 8 u W =2 .0 0 u L=0.1 8 u W =2 .0 0 u L=0.1 8 u M 8 M 3 W =2 .0 0 u L=0.1 8 u Out1 O ut2 W =2 .0 0 u L=0.1 8 u M 6 W =0 .8 0 u L=0.1 8 u M 7 W =2 .0 0 u L=0.1 8 u B M 5 W =2 .0 0 u L=0.1 8 u C M 4 W =2 .0 0 u L=0.1 8 u D M 9 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NAND4C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 3 of 4 4-Input NAND / AND Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library NAND4C Rev. A NAND4C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 4 of 4 2-Input NOR Description: NOR2 2-Input NOR Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NOR2 File: tsmc018DL.tdb Cell: NOR2 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol A Truth Table A 0 X 1 Out B Height 7.33µ Width 2.16µ B 0 1 X Area Capacitance Out 1 0 0 Equivalent Gate Drive 1X Logic Equation Out = A + B Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NOR2 Page 1 of 4 2-Input NOR NOR2 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NOR2 Page 2 of 4 2-Input NOR Schematic NOR2 NOR2 Vdd M0 W =4.0 0 u L=0 .18u M1 W =4.0 0 u L=0 .18u B A W =0.8 0 u L=0 .18u M2 W =0.8 0 u L=0 .18u Out M3 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NOR2 Page 3 of 4 2-Input NOR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. NOR2 Rev. A NOR2 Page 4 of 4 2-Input NOR / OR Description: NOR2C 2-Input NOR Gate with Complementary Output Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NOR2C File: tsmc018DL.tdb Cell: NOR2C TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol Truth Table A 0 X 1 A Out1 B Out2 Height 7.33µ Width 3.66µ B 0 1 X Out1 1 0 0 Area Capacitance Out2 0 1 1 Equivalent Gate Drive 1X Logic Equation Out1 = A + B Out2 = A + B Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NOR2C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 1 of 4 2-Input NOR / OR NOR2C This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NOR2C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 2 of 4 2-Input NOR / OR Schematic NOR2C NOR2C Vdd B M0 W =4.0 0 u L=0.18u M5 W =4.0 0 u L=0.18u Out1 A M1 W =2.0 0 u L=0.18u W =0.8 0 u L=0.18u M2 W =0.8 0 u L=0.18u M3 Out2 W =0.8 0 u L=0.18u M4 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NOR2C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 3 of 4 2-Input NOR / OR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library NOR2C Rev. A NOR2C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 4 of 4 3-Input NOR Description: NOR3 3-Input NOR Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NOR3 File: tsmc018DL.tdb Cell: NOR3 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol A B C Truth Table A 0 X X 1 Out Height 7.33µ Width 5.76µ B 0 X 1 X C 0 1 X X Area Capacitance Out 1 0 0 0 Equivalent Gate Drive 1X Logic Equation Out = A + B + C Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NOR3 Page 1 of 4 3-Input NOR NOR3 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NOR3 Page 2 of 4 3-Input NOR Schematic NOR3 NOR3 Vdd C B A M4 W=6.00u L=0.18u M0 W=6.00u L=0.18u M1 W=6.00u L=0.18u W=0.80u L=0.18u M2 W=0.80u L=0.18u M3 W=0.80u L=0.18u Out M5 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NOR3 Page 3 of 4 3-Input NOR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. NOR3 Rev. A NOR3 Page 4 of 4 3-Input NOR / OR Description: NOR3C 3-Input NOR Gate with Complementary Output Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NOR3C File: tsmc018DL.tdb Cell: NOR3C TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol A B C Truth Table A 0 X X 1 Out1 Out2 Height 7.33µ Width 7.20µ B 0 X 1 X C 0 1 X X Capacitance Out1 1 0 0 0 Area Out2 0 1 1 1 Equivalent Gate Drive 1X Logic Equation Out1 = A + B + C Out2 = A + B + C Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NOR3C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 1 of 4 3-Input NOR / OR NOR3C This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NOR3C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 2 of 4 3-Input NOR / OR Schematic NOR3C NOR3C Vdd C W =6.0 0 u L=0.18u T1 1 B T2 W =6.0 0 u L=0.18u Out1 2 A T3 W =6.0 0 u L=0.18u W =0.8 0 u L=0.18u A T4 T7 W =0.8 0 u L=0.18u B T5 W =0.8 0 u L=0.18u C T6 W =2.0 0 u L=0.18u W =0.8 0 u L=0.18u Out2 T8 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NOR3C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 3 of 4 3-Input NOR / OR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library NOR3C Rev. A NOR3C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 4 of 4 4-Input NOR Description: NOR4 4-Input NOR Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NOR4 File: tsmc018DL.tdb Cell: NOR4 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol A B Truth Table A 0 X X X 1 Out C D Height 7.33µ Width 7.92µ B 0 X X 1 X C 0 X 1 X X D 0 1 X X X Area Capacitance Out 1 0 0 0 0 Equivalent Gate Drive 1X Logic Equation Out = A + B + C + D Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NOR4 Page 1 of 4 4-Input NOR NOR4 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NOR4 Page 2 of 4 4-Input NOR Schematic NOR4 NOR4 Vdd D C M6 W=8.00u L=0.18u M4 W=8.00u L=0.18u M0 W=8.00u L=0.18u M1 W=8.00u L=0.18u B A W=0.80u L=0.18u M2 W=0.80u L=0.18u M3 W=0.80u L=0.18u M5 W=0.80u L=0.18u Out M7 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A NOR4 Page 3 of 4 4-Input NOR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. NOR4 Rev. A NOR4 Page 4 of 4 4-Input NOR / OR Description: NOR4C 4-Input NOR Gate with Complementary Output Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: NOR4C File: tsmc018DL.tdb Cell: NOR4C TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol Truth Table A 0 X X X 1 A B Out1 C D Out2 Height 7.33µ Width 9.36µ B 0 X X 1 X C 0 X 1 X X D 0 1 X X X Capacitance Out1 1 0 0 0 0 Area Out2 0 1 1 1 1 Equivalent Gate Drive 1X Logic Equation Out1 = A + B + C + D Out2 = A + B + C + D Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NOR4C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 1 of 4 4-Input NOR / OR NOR4C This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NOR4C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 2 of 4 4-Input NOR / OR Schematic NOR4C NOR4C Vdd D W =8.00u L=0.18u T1 1 C W =8.00u L=0.18u T2 2 B W =8.00u L=0.18u T3 Out1 3 A T4 W =8.00u L=0.18u W =0.80u L=0.18u A T5 W =2.00u L=0.18u T9 W =0.80u L=0.18u B T6 W =0.80u L=0.18u C W =0.80u L=0.18u D T7 T8 W =0.80u L=0.18u Out2 T10 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A NOR4C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 3 of 4 4-Input NOR / OR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library NOR4C Rev. A NOR4C Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 4 of 4 Schmitt Trigger Inverter Description: Schmitt Trigger Inverter Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Logic Symbol A SINV Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: SINV File: tsmc018DL.tdb Cell: SINV TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Truth Table A 0 1 Y Height 7.33µ Width 3.60µ Capacitance Y 1 0 Area Equivalent Gate Drive 1X Logic Equation Out = A Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A SINV Page 1 of 4 Schmitt Trigger Inverter SINV This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A SINV Page 2 of 4 Schmitt Trigger Inverter Schematic SINV Schmitt Trigger Inverter Vdd T4 W=2.00u L=0.18u M=1 T5 T6 1 L=0.18u W=2.00u Vdd W=2.00u L=0.18u Gnd Out Vdd M=1 A T2 M=1 T3 W=0.80u L=0.18u 3 T1 W=0.80u L=0.18u W=0.80u L=0.18u Gnd Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A SINV Page 3 of 4 Schmitt Trigger Inverter Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. SINV Rev. A SINV Page 4 of 4 2-Input Exclusive-NOR Description: XNOR2 2-Input Exclusive-NOR Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: XNOR2 File: tsmc018DL.tdb Cell: XNOR2 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol Truth Table A 0 0 1 1 A Out B Height 7.33µ Width 4.32µ B 0 1 0 1 Area Capacitance Out 1 0 0 1 Equivalent Gate Drive 1X Logic Equation Out = (A × B) + ( A × B) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A XNOR2 Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 1 of 4 2-Input Exclusive-NOR XNOR2 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A XNOR2 Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 2 of 4 2-Input Exclusive-NOR Schematic XNOR2 XNOR2 Vdd T1 W =2 .0 0 uW =2 .0 0 u L=0 .18u L=0 .18u T2 W =2 .0 0 u L=0 .18u T5 T9 3 A B W =2 .0 0 u L=0 .18u W =2 .0 0 u L=0 .18u Out T6 W =0 .8 0 u 1 L=0 .18u T3 2 W =0 .8 0 uW =0 .8 0 u L=0 .18u L=0 .18u W =0 .8 0 u L=0 .18u T1 0 B 4b T4 T7 T1 0 W =0 .8 0 uW =0 .8 0 u L=0 .18u L=0 .18u 4 T8 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Rev. A XNOR2 Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 3 of 4 2-Input Exclusive-NOR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library XNOR2 Rev. A XNOR2 Copyright 2000 by Tanner Research, Inc. All rights reserved. Page 4 of 4 2-Input Exclusive-OR Description: XOR2 2-Input Exclusive-OR Gate Library: Tanner tsmc018DL Schematic: S-Edit Mask layout: L-Edit Mapping Macros: GateSim: L-Edit/SPR: Primitive Set: Tanner SCMOS.Cells Tanner.TIB.Samples File: tsmc018DL.sdb Module: XOR2 File: tsmc018DL.tdb Cell: XOR2 TannerLb\nettran\scmos\scms2sim.mac TannerLb\nettran\scmos\scms2tpr.mac Logic Symbol Truth Table A 0 0 1 1 A Out B Height 7.33µ Width 4.32µ B 0 1 0 1 Area Capacitance Out 0 1 1 0 Equivalent Gate Drive 1X Logic Equation Out = (A × B) + ( A × B) Delay Characteristics: TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A XOR2 Page 1 of 4 2-Input Exclusive-OR XOR2 This page is intentionally left blank. TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A XOR2 Page 2 of 4 2-Input Exclusive-OR Schematic XOR2 XOR2 Vdd W =2.00u L=0.18u T3 T4 W =2.00u L=0.18u T7 W =2.00uW =2.00u L=0.18u L=0.18u T8 T10B W =2.00uW =2.00u L=0.18u L=0.18u T10 W =0.80u L=0.18u Out T9 A B W =0.80u L=0.18u W =0.80uW =0.80u L=0.18u L=0.18u T1 T6 T2 W =0.80u L=0.18u T5 Gnd TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. Rev. A XOR2 Page 3 of 4 2-Input Exclusive-OR Layout TSMC 0.18µ µm – tsmc018DL Digital Standard Cell Library Copyright 2000 by Tanner Research, Inc. All rights reserved. XOR2 Rev. A XOR2 Page 4 of 4

0

0

advertisement

Related documents

Download

advertisement

Add this document to collection(s)

You can add this document to your study collection(s)

Sign in Available only to authorized usersAdd this document to saved

You can add this document to your saved list

Sign in Available only to authorized users