FEATURES

GENERAL DESCRIPTION

Enhanced product features

Supports defense and aerospace applications (AQEC)

Military temperature range (−55°C to +125°C)

Controlled manufacturing baseline

One assembly/test site

One fabrication site

Enhanced product change notification

Qualification data available on request

4 buffered 12-Bit DACs in 10-lead MSOP

S Version: ±10 LSB INL

Low power operation: 500 μA @ 3 V, 600 μA @ 5 V

2.5 V to 5.5 V power supply

Guaranteed monotonic by design over all codes

Power-down to 80 nA @ 3 V, 200 nA @ 5 V

Double-buffered input logic

Output range: 0 V to VREF

Power-on reset to 0 V

Simultaneous update of outputs (LDAC function)

On-chip, rail-to-rail output buffer amplifiers

Temperature range –55°C to +125°C

The AD5324-EP1 is a quad 12-bit buffered voltage output DAC

in a 10-lead MSOP package that operates from a single 2.5 V to

5.5 V supply, consuming 500 μA at 3 V. Its on-chip output

amplifiers allows rail-to-rail output swing to be achieved with a

slew rate of 0.7 V/μs. A 3-wire serial interface is used; it operates

at clock rates up to 30 MHz and is compatible with standard SPI,

QSPI™, MICROWIRE™, and DSP interface standards.

The references for the four DACs are derived from one reference

pin. The outputs of all DACs can be updated simultaneously using

the software LDAC function. The part incorporates a power-on

reset circuit, and ensures that the DAC outputs power up to 0 V

and remains there until a valid write takes place to the device.

The part contains a power-down feature that reduces the current

consumption of the device to 200 nA at 5 V (80 nA at 3 V).

The low power consumption of this part in normal operation

makes it ideally suited to portable battery-operated equipment. The

power consumption is 3 mW at 5 V, and 1.5 mW at 3 V, reducing

to 1 μW in power-down mode.

Full details about this enhanced product are available in the

AD5324 data sheet, which should be consulted in conjunction

with this data sheet.

APPLICATIONS

Portable battery-powered instruments

Digital gain and offset adjustment

Programmable voltage and current sources

Programmable attenuators

Industrial process control

1

Protected by U.S. Patent No. 5,969,657; other patents pending.

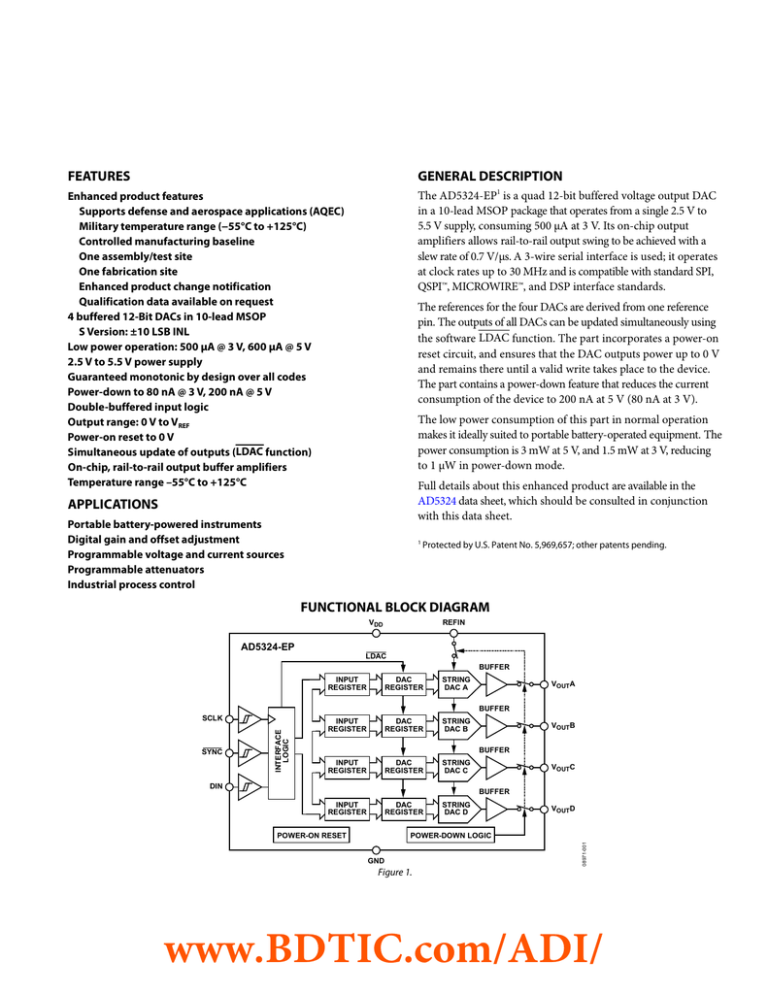

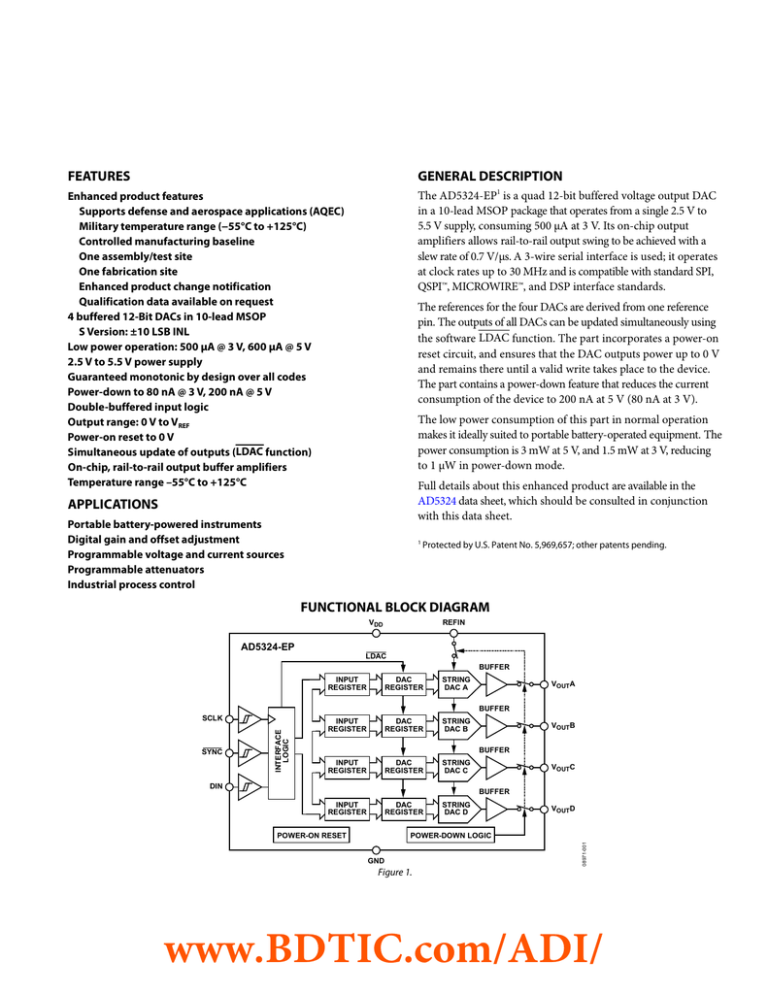

FUNCTIONAL BLOCK DIAGRAM

VDD

REFIN

AD5324-EP

LDAC

BUFFER

INPUT

REGISTER

DAC

REGISTER

STRING

DAC A

INPUT

REGISTER

DAC

REGISTER

STRING

DAC B

INPUT

REGISTER

DAC

REGISTER

STRING

DAC C

INPUT

REGISTER

DAC

REGISTER

STRING

DAC D

VOUTA

BUFFER

VOUTB

BUFFER

DIN

VOUTC

BUFFER

POWER-ON RESET

VOUTD

POWER-DOWN LOGIC

GND

08971-001

SYNC

INTERFACE

LOGIC

SCLK

Figure 1.

www.BDTIC.com/ADI/

TABLE OF CONTENTS

Features .............................................................................................. 1

Timing Characteristics .................................................................5

Applications ....................................................................................... 1

Absolute Maximum Ratings ............................................................6

General Description ......................................................................... 1

ESD Caution...................................................................................6

Functional Block Diagram .............................................................. 1

Pin Configuration and Function Descriptions..............................7

Revision History ............................................................................... 2

Typical Performance Characteristics ..............................................8

Specifications..................................................................................... 3

Outline Dimensions ....................................................................... 11

AC Characteristics ........................................................................ 4

Ordering Guide .......................................................................... 11

REVISION HISTORY

4/10—Revision 0: Initial Version

www.BDTIC.com/ADI/

SPECIFICATIONS

VDD = 2.5 V to 5.5 V; VREF = 2 V; RL = 2 kΩ to GND; CL = 200 pF to GND; all specifications TMIN to TMAX, unless otherwise noted.

Table 1.

Parameter

DC PERFORMANCE1

Resolution

Relative Accuracy

Differential Nonlinearity2

Offset Error

Gain Error

Lower Dead Band

Offset Error Drift3

Gain Error Drift3

DC Power Supply Rejection Ratio3

DC Crosstalk3

DAC REFERENCE INPUTS3

VREF Input Range

VREF Input Impedance

Min

S Version

Typ

12

±2

±0.2

±0.4

±0.15

20

–12

–5

–60

200

0.25

37

Reference Feedthrough

OUTPUT CHARACTERISTICS3

Minimum Output Voltage4

Maximum Output Voltage4

DC Output Impedance

Short Circuit Current

VDD

45

>10

–90

LOGIC INPUTS3

Input Current

VIL, Input Low Voltage

Pin Capacitance

POWER REQUIREMENTS

VDD

IDD (Normal Mode)5

VDD = 4.5 V to 5.5 V

VDD = 2.5 V to 3.6 V

IDD (Power-Down Mode)

VDD = 4.5 V to 5.5 V

VDD = 2.5 V to 3.6 V

±10

±1

±3

±1

60

0.001

VDD – 0.001

0.5

25

16

2.5

5

Power-Up Time

VIH, Input High Voltage

Max

Unit

Bits

LSB

LSB

% of FSR

% of FSR

mV

ppm of FSR/°C

ppm of FSR/°C

dB

μV

V

kΩ

MΩ

dB

V

Ω

mA

mA

μs

μs

Conditions/Comments

Guaranteed monotonic by design over all codes

See Figure 2

See Figure 2

Lower dead band exists only if offset error is negative

ΔVDD = ±10%

RL = 2 kΩ to GND or VDD

Normal operation

Power-down mode

Frequency = 10 kHz

Measurement of the minimum and maximum

V drive capability of the output amplifier

VDD = 5 V

VDD = 3 V

Coming out of power-down mode VDD = 5 V

Coming out of power-down mode VDD = 3 V

±1

0.8

0.6

0.5

μA

V

V

V

V

V

V

pF

5.5

V

600

500

900

700

μA

μA

VIH = VDD and VIL = GND

VIH = VDD and VIL = GND

0.2

0.08

1

1

μA

μA

VIH = VDD and VIL = GND

VIH = VDD and VIL = GND

2.4

2.1

2.0

3

2.5

VDD = 5 V ± 10%

VDD = 3 V ± 10%

VDD = 2.5 V

VDD = 5 V ± 10%

VDD = 3 V ± 10%

VDD = 2.5 V

1

DC specifications tested with the outputs unloaded.

Linearity is tested using a reduced code range: Code 115 to Code 3981.

Guaranteed by design and characterization, not production tested.

4

For the amplifier output to reach its minimum voltage, offset error must be negative. For the amplifier output to reach its maximum voltage, VREF = VDD and offset plus

gain error must be positive.

5

IDD specification is valid for all DAC codes; interface inactive; all DACs active; load currents excluded.

2

3

www.BDTIC.com/ADI/

AC CHARACTERISTICS

VDD = 2.5 V to 5.5 V; RL = 2 kΩ to GND; CL = 200 pF to GND; all specifications TMIN to TMAX, unless otherwise noted.

Table 2.

1

Parameter

Output Voltage Settling Time

S Version2

Min

Typ

Max

Slew Rate

Major-Code Transition Glitch Energy

Digital Feedthrough

Digital Crosstalk

DAC-to-DAC Crosstalk

Multiplying Bandwidth

Total Harmonic Distortion

1

2

8

0.7

12

1

1

3

200

–70

10

Unit

μs

V/μs

nV-sec

nV-sec

nV-sec

nV-sec

kHz

dB

Conditions/Comments

VREF = VDD = 5 V

¼ scale to ¾ scale change (0x400 to 0xC00)

1 LSB change around major carry

VREF = 2 V ± 0.1 V p-p

VREF = 2.5 V ± 0.1 V p-p; frequency = 10 kHz

Guaranteed by design and characterization, not production tested.

Temperature range (S Version): −55°C to +125°C; typical at +25°C.

www.BDTIC.com/ADI/

TIMING CHARACTERISTICS

VDD = 2.5 V to 5.5 V; all specifications TMIN to TMAX, unless otherwise noted.

Table 3.

Parameter1, 2, 3

t1

t2

t3

t4

t5

t6

t7

t8

2

3

Unit

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

Conditions/Comments

SCLK cycle time

SCLK high time

SCLK low time

SYNC to SCLK falling edge setup time

Data setup time

Data hold time

SCLK falling edge to SYNC rising edge

Minimum SYNC high time

Guaranteed by design and characterization, not production tested.

All input signals are specified with tr = tf = 5 ns (10% to 90 % of VDD) and timed from a voltage level of (VIL + VIH)/2.

See Figure 2.

t1

SCLK

t8

t3

t4

t2

t7

SYNC

t6

DIN

DB15

t5

DB0

Figure 2. Serial Interface Timing Diagram

www.BDTIC.com/ADI/

00929-002

1

Limit at TMIN, TMAX

VDD = 2.5 V to 3.6 V

VDD = 3.6 V to 5.5 V

40

33

16

13

16

13

16

13

5

5

4.5

4.5

0

0

80

33

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 4.

Parameter1

VDD to GND

Digital Input Voltage to GND

Reference Input Voltage to GND

VOUTA through VOUTD to GND

Operating Temperature Range

Industrial (EP Version)

Storage Temperature Range

Junction Temperature (TJ max)

10-Lead MSOP

Power Dissipation

θJA Thermal Impedance

θJC Thermal Impedance

Reflow Soldering

Peak Temperature

Time at Peak Temperature

1

Rating

–0.3 V to +7 V

–0.3 V to VDD + 0.3 V

–0.3 V to VDD + 0.3 V

–0.3 V to VDD + 0.3 V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

–55°C to +125°C

–65°C to +150°C

150°C

(TJ max – TA)/ θJA

206°C/W

44°C/W

220°C

10 sec to 40 sec

Transient currents of up to 100 mA do not cause SCR latch-up.

www.BDTIC.com/ADI/

VDD 1

10

SYNC

VOUTA 2

9

SCLK

VOUTB 3

VOUTC 4

REFIN 5

AD5324-EP

TOP VIEW

(Not to Scale)

8

DIN

7

GND

6

VOUTD

08971-003

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. MSOP Pin Configuration

Table 5. Pin Function Descriptions

Pin No.

1

2

3

4

5

6

7

8

Mnemonic

VDD

VOUTA

VOUTB

VOUTC

REFIN

VOUTD

GND

DIN

9

SCLK

10

SYNC

Description

Power Supply Input. This part can be operated from 2.5 V to 5.5 V and the supply can be decoupled to GND.

Buffered Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.

Buffered Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.

Buffered Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.

Reference Input Pin for All Four DACs. It has an input range from 0.25 V to VDD.

Buffered Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.

Ground Reference Point for All Circuitry on the Part.

Serial Data Input. This device has a 16-bit shift register. Data is clocked into the register on the falling edge of the

serial clock input. The DIN input buffer is powered down after each write cycle.

Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can

be transferred at clock speeds up to 30 MHz. The SCLK input buffer is powered down after each write cycle.

Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes low, it

enables the input shift register and data is transferred in on the falling edges of the following 16 clocks. If SYNC is

taken high before the 16th falling edge of SCLK, the rising edge of SYNC acts as an interrupt and the write

sequence is ignored by the device.

www.BDTIC.com/ADI/

TYPICAL PERFORMANCE CHARACTERISTICS

12

2.0

TA = 25°C

VDD = 5V

MAX INL

1.5

8

ERROR (LSB)

INL ERROR (LSB)

1.0

4

0

MAX DNL

0.5

MIN DNL

0

0.5

–4

1.0

–8

500

1000

1500

2000

2500

3000

3500

4000

CODE

2.0

80

40

20

0

20

60

40

80

100

120

140

6

TEMPERATURE (°C)

Figure 7. INL and DNL Error vs. Temperature

Figure 4. Typical INL Plot

1.0

0.2

TA = 25°C

VDD = 5V

TA = 25°C

VREF = 2V

0.1

0.5

GAIN ERROR

0

ERROR (%)

DNL ERROR (LSB)

60

08971-023

0

08971-004

–12

08971-008

MIN INL

1.5

0

–0.5

–0.1

–0.2

–0.3

–0.4

OFFSET ERROR

–0.5

0

500

1000

1500

2000

2500

3000

3500

4000

CODE

–0.6

08971-005

–1.0

0

1

2

3

Figure 5. Typical DNL Plot

5

Figure 8. Offset Error and Gain Error vs. VDD

0.8

5

0.7

5V SOURCE

0.6

4

GAIN ERROR

0.5

VOUT (V)

0.4

0.3

0.2

3V SOURCE

3

2

0.1

5V SINK

3V SINK

OFFSET ERROR

0

1

–0.2

–80

–60

–40

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

Figure 6. Offset Error and Gain Error vs. Temperature

140

0

0

1

2

3

4

5

SINK/SOURCE CURRENT (mA)

Figure 9. VOUT Source and Sink Current Capability

www.BDTIC.com/ADI/

6

08971-009

–0.1

08971-022

ERROR (%)

4

VDD (V)

600

1000

TA = 25°C

VDD = 5V

VREF = 2V

500

TA = 25°C

900

800

IDD (µA)

IDD (µA)

400

300

VDD = 5V

700

600

200

VDD = 3V

500

100

FULL SCALE

CODE

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

VLOGIC (V)

Figure 10. Supply Current vs. DAC Code

Figure 13. Supply Current vs. Logic Input Voltage

600

TA = 25°C

VDD = 5V

VREF = 5V

–40°C

500

CH1

+25°C

400

VOUTA

IDD (µA)

+105°C

300

SCLK

200

CH2

3.0

3.5

4.0

4.5

5.0

5.5

VDD (V)

CH1 1V, CH2 5V, TIME BASE = 1µs/DIV

08971-011

0

2.5

08971-014

100

Figure 14. Half-Scale Settling (¼ to ¾ Scale Code Change)

Figure 11. Supply Current vs. Supply Voltage

0.5

TA = 25°C

VDD = 5V

VREF = 2V

CH1

VDD

CH2

VOUTA

0.3

–40°C

0.2

+25°C

0.1

0

2.5

3.0

3.5

4.0

4.5

5.0

VDD (V)

Figure 12. Power-Down Current vs. Supply Voltage

5.5

CH1 2V, CH2 200mV, TIME BASE = 200µs/DIV

Figure 15. Power-On Reset to 0 V

www.BDTIC.com/ADI/

08971-015

+105°C

08971-012

IDD (µA)

0.4

08971-013

ZERO SCALE

08971-010

400

0

10

TA = 25°C

VDD = 5V

VREF = 2V

0

–10

VOUTA

CH1

(dB)

–20

–30

CH2

SCLK

–40

CH1 500mV, CH2 5V, TIME BASE = 1µs/DIV

–60

10

100

1k

10k

100k

1M

10M

FREQUENCY (Hz)

Figure 16. Exiting Power-Down to Midscale

08971-019

08971-016

–50

Figure 19. Multiplying Bandwidth (Small-Signal Frequency Response)

0.02

350

400

450

500

550

600

IDD (µA)

0.01

0

–0.01

–0.02

0

1

2

3

4

5

6

VREF (V)

Figure 17. IDD Histogram with VDD = 3 V and VDD = 5 V

Figure 20. Full-Scale Error vs. VREF

2.50

VOUT (V)

1mV/DIV

2.49

1µs/DIV

Figure 18. Major-Code Transition Glitch Energy

150ns/DIV

Figure 21. DAC-to-DAC Crosstalk

www.BDTIC.com/ADI/

08971-021

2.47

08971-018

2.48

08971-020

300

VDD = 5V

08971-017

FREQUENCY

VDD = 3V

FULL-SCALE ERROR (V)

VDD = 5V

TA = 25°C

OUTLINE DIMENSIONS

3.10

3.00

2.90

6

10

3.10

3.00

2.90

1

5.15

4.90

4.65

5

PIN 1

0.50 BSC

0.95

0.85

0.75

1.10 MAX

0.15

0.05

0.33

0.17

SEATING

PLANE

0.23

0.08

8°

0°

0.80

0.60

0.40

COPLANARITY

0.10

COMPLIANT TO JEDEC STANDARDS MO-187-BA

Figure 22. 10-Lead Mini Small Outline Package [MSOP]

(RM-10)

Dimensions shown in millimeters

ORDERING GUIDE

Model1

AD5324SRMZ-EP-RL7

1

Temperature Range

–55°C to +125°C

Package Description

10-Lead Mini Small Outline Package (MSOP)

Package Option

RM-10

Z = RoHS Compliant Part.

www.BDTIC.com/ADI/

Branding

DFT

NOTES

©2010 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D08971-0-4/10(0)

www.BDTIC.com/ADI/