What is time constant, τ?

advertisement

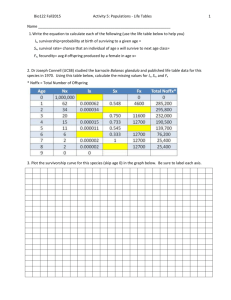

Delay is RC Charging ESE370: Circuit-Level Modeling, Design, and Optimization for Digital Systems Lec 5: September 11, 2015 Delay and RC Response Penn ESE370 Fall2015 – Khanna Penn ESE370 Fall2015 – Khanna Delay is RC Charging Today Strategy: ! Use zero-order model to understand switch state ! Break into output/ input stages ! For each stage " " 2 ! RC Charging ! What is the C? " " RC Step Response Curve Capacitive Load on Gate Output ! What is the R? ! Approximating and Measuring Delay " Equivalent Output Resistance Understand Rdrive Understand Cload Penn ESE370 Fall2015 – Khanna 3 90% Rise Time? 4 What does response look like? What is time constant, τ? Penn ESE370 Fall2015 – Khanna Penn ESE370 Fall2015 – Khanna ~ 2ps for 90% rise 5 Penn ESE370 Fall2015 – Khanna 6 1 Governing Equations? (KCL) Governing Equations? (KCL) IR IC ! KCL @ Vmeasure " ! Kirchoff’s Current Law " " KCL @ Vmeasure " Sum of all currents into a node = 0 Current entering a node = current exiting a node " " " Penn ESE370 Fall2015 – Khanna Kirchoff’s Current Law 7 Governing Equations? (KCL) Sum of all currents into a node = 0 Current entering a node = current exiting a node IR=IC Penn ESE370 Fall2015 – Khanna 8 Governing Equations? (KCL) IR IR IC IC I R = IC I R = IC dV VR =C C R dt Vin −Vmeasure dVmeasure =C R dt dV VR =C C R dt Vin −Vmeasure dVmeasure =C R dt Penn ESE370 Fall2015 – Khanna 9 What does look like? 0= dVmeasure 1 V + V − in dt RC measure RC ( Vmeasure = Vin 1− ( e−t/RC ) τ = RC Penn ESE370 Fall2015 – Khanna ) 10 Shape of Curve t (in ps) e-t/RC 1-e-t/RC 0 0.1 1 2 2.3 ( Vmeasure = Vin 1− ( e−t/RC ) Penn ESE370 Fall2015 – Khanna Vin=1 ) 11 ( Vmeasure = Vin 1− ( e−t/RC ) Penn ESE370 Fall2015 – Khanna ) 12 2 Shape of Curve Rise Time: 10—90% t (in ps) e-t/RC 0 0.1 1 2 2.3 1 0.9 1/e = 0.37 1/e2 = 0.14 0.1 1-e-t/RC ( 0 0.1 10% 0.66 0.86 0.9 90% Vmeasure = Vin 1− ( e−t/RC ) Vin=1 ) Penn ESE370 Fall2015 – Khanna Trise ~= 2.2ps ~= 2.2τ 13 Penn ESE370 Fall2015 – Khanna 14 Rise Time: 10—90% What is C? τ=RC Trise ~= 2.2ps ~= 2.2τ Penn ESE370 Fall2015 – Khanna 15 Capacitance ! ! 16 Fanout Wire Fanout -- Total gate load " Penn ESE370 Fall2015 – Khanna ! Number of things to which a gate output connects Logical Gate " MOSFET gate Penn ESE370 Fall2015 – Khanna 17 Penn ESE370 Fall2015 – Khanna 18 3 Fanout in Circuit ! Fanout in Circuit Output routed to many gate inputs ! ! ! Penn ESE370 Fall2015 – Khanna 19 Fanout in Circuit ! ! ! Maximum fanout? Second? Min? Penn ESE370 Fall2015 – Khanna 20 Fanout in Circuit Maximum fanout? Second? Min? ! ! ! Maximum fanout? Second? Min? 2 3 3 Penn ESE370 Fall2015 – Khanna 21 Fanout in Circuit ! ! ! Maximum fanout? Second? Min? Penn ESE370 Fall2015 – Khanna Penn ESE370 Fall2015 – Khanna 22 Fanout in Circuit ! ! 1 1 1 3 ! 1 Maximum fanout? Second? Min? 1 1 2 1 2 1 1 3 1 23 Penn ESE370 Fall2015 – Khanna 0 0 24 4 MOSFET Capacitance ! First Order Model “load of 1”? " Capacitive 2 2 1 1 Out A 2 1 ! Switch 2 B 1 " Penn ESE370 Fall2015 – Khanna 25 MOSFET Capacitance ! Loads input capacitively Penn ESE370 Fall2015 – Khanna 26 First Order Model “load of 1”? " Capacitive 2 2 1 1 Out A 2 ! Switch ! As we dig into the device structure understand: 1 2 B 1 " " " " Penn ESE370 Fall2015 – Khanna 27 Loads input capacitively Origin of capacitance How to engineer device parameters like Cg, RON, Vth Tradeoffs Penn ESE370 Fall2015 – Khanna 28 Lumped Capacitive Load What is R? Cload = ∑C i∈ fanout € Penn ESE370 Fall2015 – Khanna gi + ∑C wi i∈wires 29 Penn ESE370 Fall2015 – Khanna 30 5 Resistance ! ! Switch ! As we dig into the device structure understand: Wire resistance " " ! First Order Model " From supply (Vdd or Gnd) to transistor source From transistor output to gate it is driving " Transistor equivalent resistance (Ron) " " Penn ESE370 Fall2015 – Khanna 31 Resistive driver More sophisticated view, not just RON How to engineer device parameters like Cg, RON, Vth Tradeoffs Penn ESE370 Fall2015 – Khanna Equivalent Resistance 32 Equivalent Resistance ! What resistances might transistors contribute? " 2 2 1 1 " How many cases? Assume Ron=Ron,p=Ron,n 2 2 1 1 Out Out A A 2 2 1 1 2 B 2 B 1 Penn ESE370 Fall2015 – Khanna 33 Penn ESE370 Fall2015 – Khanna Equivalent Resistance ! " ! How many cases? Assume Ron=Ron,p=Ron,n 34 Equivalent Resistance What resistances might transistors contribute? " 1 What resistances might transistors contribute? " 2 2 1 1 " How many cases? Assume Ron=Ron,p=Ron,n 2 2 1 1 Out Out A Input Rout A 2 2 1 1 Input Rout 00 00 Ron/2 01 01 Ron 10 10 Ron 11 11 2Ron Penn ESE370 Fall2015 – Khanna 2 B 1 35 Penn ESE370 Fall2015 – Khanna 2 B 1 36 6 Rise/Fall Times ! Lumped Resistive Source Rise and Fall time may differ " " Why? What is ratio? 2 2 1 1 Rdrive = Rtr,net + Out " ∑ Rwi i∈wires A 2 1 Input Rout 00 Ron/2 01 Ron 10 Ron 11 2Ron 2 B 1 Rtr,net = transistor network resistance = parallel and series combination of Rtr Penn ESE370 Fall2015 – Khanna 37 Penn ESE370 Fall2015 – Khanna 38 Voltage Waveform at Input/Output Node Measuring Delay Rdrive from output stages and wires CLoad from input stages and wires Penn ESE370 Fall2015 – Khanna 39 Measuring Gate Delay Penn ESE370 Fall2015 – Khanna Characterizing Gate/Technology ! 67ps 80ps tdel = 13ps Delay measure will be " " Function of load on gate Function of input rise time " ! ! 40 Which, in turn, may be a function of input loading Next stage starts to switch before first finishes Measure from 50% of input swing to 50% of output swing Penn ESE370 Fall2015 – Khanna 41 Penn ESE370 Fall2015 – Khanna 42 7 Delay vs. Risetime 1ps rise Characterizing Gate/Technology 100ps rise ! Delay measure will be " " Function of load on gate Function of input rise time " ! " 10ps delay ! If we didn’t know the input rise time, we wouldn’t know what a 13ps delay meant 43 Penn ESE370 Fall2015 – Khanna 44 HW3 Measurement Setup Standard Measurement for Characterization Drive with a gate " " ! Allows us to compare designs with a (somewhat) normalized delay metric 20ps delay Penn ESE370 Fall2015 – Khanna ! Which, in turn, may be a function of input loading Want to understand typical delay times Not an ideal source Input rise time typically would see in circuit Measure loaded gate " Typical loading – FO4 Function Generator Oscilloscope Not realistic measurement Penn ESE370 Fall2015 – Khanna 45 Measurement for Characterization ! " ! ! Not an ideal source (how does delay change if drive is ideal?) Input rise time typically would see in circuit " ! 47 Not an ideal source Input rise time typically would see in circuit Measure loaded gate " Typical loading – FO4 Penn ESE370 Fall2015 – Khanna Drive with a gate " Measure loaded gate " 46 Measurement for Characterization Drive with a gate " Penn ESE370 Fall2015 – Khanna Typical loading – FO4 (how does delay change if gate is unloaded?) Penn ESE370 Fall2015 – Khanna 48 8 Delay is RC Charging Admin ! “Normal Week” " " ! 3 Lecture Week (all here) MOS Operation and Devices Spice Flow " Penn ESE370 Fall2015 – Khanna 49 access to electric, setup for spice, run ngspice Penn ESE370 Fall2015 – Khanna 50 Admin ! “Normal Week” " " 3 Lecture Week (all here) MOS Operation and Devices ! Spice Flow ! HW quality " " " " ! access to electric, setup for spice, run ngspice Show your work Label axes, explain your results If we can’t understand it, we can’t grade it HW turnin " Must turn in by the time I start lecturing (12:05) " Won’t accept any more after that Penn ESE370 Fall2015 – Khanna 51 9